9.1 逻辑闸 IC, 二元布尔代代数学和数字电子技巧

专为模拟讯号而设计之运算放大器集成电路 (i) 可处理线性数学比例放大或 (ii) 非线性数学函数如积分、微分、振荡等。 电字逻辑闸IC (digital logic gate IC) 则全部设计为处理 (0 1) 二进制元而进行基于布尔二元表达式 (binary Boolean expressions) 之数字计算。两类电子组件属于两门完全不同电子科技范畴。它们发展起步时间相若,但电字逻辑闸IC很快便抛离运算放大器IC,发展成为更先进和更成熟电子科技。现时逻辑闸集成电路重要性远高于线性集成电路 IC。

逻辑闸 IC 专门用在数字电路设计,应用范围很广。不但民用方面持续发展和增长,更在军用和太空科技方面有不可取代之重要性。讯号数字 (码) 化后产生游离 (discrete) 高低讯号链,即 (0 1) 位,其处理之可能性和方法极多,应用于多不胜数产品上,如智能手机、计算机、数码相机、音响、电视机、广告牌等等。昔日影像和声音之播放只可以用模拟电路录像带和拾影/音磁头,但现在录像带已在市场消失,取而代之是数字播放器。例如压缩数字讯号 MP3、MPEG 4、JPEG、AVI、MK、FLV、DVD、MOV、WMV等译码器,都需要逻辑闸集成电路始可运作。

(i) 数字 (二进制元组)逻辑和布尔代数学 (Binary Boolean algebra and binary digital logic)

以十进数字 0 至 9 代入传统代数方程式可得计算结果。但电子计算世界只有1 (高压,5 V) 和 0 (低压,0 V) 两种数字,因此有需要建立另一种代数学,只能代入 1 和 0 两个可能数字。这种代数学叫布尔代数学 (Boolean algebra) 。

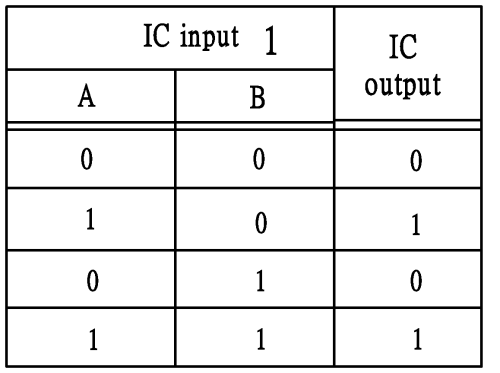

代入最简单的传统代数方程式 A + B = C,若A = 1, B = 2 即得 C = 3,若 A= 2, B = 3 则 C = 5,如此类推。若方程式以布尔代数演绎,只可以写作A + B = A 或 A + B = B。因所有布尔变量只可以有 1 值或 0 值。若以电子电路演绎,就是一起两端输入 (0 0) 、(0 1) 、(1 0) 或 (1 1),因二进 (0 1) 比特有 22 或4种变化,输出单端 1 或 0。布尔逻辑衍生真值表 (truth table) (图 237):

| A | B | A+B = A |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 1 | 1 |

| A | B | A+B = B |

| 0 | 0 | 0 |

| 1 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 1 | 1 |

(图 237) 真值表

以上只是数学逻辑讨论。要布尔代数1值和0值与数字讯号产生联动关系便需要电子电路去演绎,这类电路叫电子逻辑闸 (logic gate)。布尔操作数 (Boolean operator) 之OR (+),AND (。) 或 NOT ( — ) 等皆可以电子逻辑闸演绎。

(ii) 电子逻辑闸 (Electronic logic gate)

电子逻辑闸有两大类: (i) 早期之TTL (transistor-transistor logic) 和 (ii) 后来之CMOS (complementary metal oxide semiconductor) 。

| 各种电逻辑闸: |  | 等 | |||

AND | NAND | NOT | OR |

(iii) TTL电子逻辑闸

晶体管-晶体管逻辑 (Transistor-Transistor Logic,缩写为 TTL) ,是开发和上市较早的电子逻辑闸集成电路。顾名思义,TTL 每一单位以npn 双晶体管直接耦合组成。常用零件编号为 74 xx 系列 (民用)。

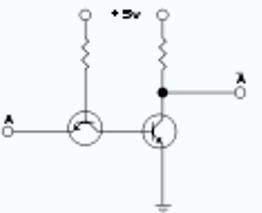

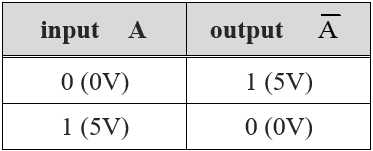

(图 238) 一单位TTL反相器

如 (图238) 所示,左边npn晶体管发射极 (emitter) 作为输入端 (A) 。只要接上髙压 (5V) ,微少电流直通集电极 (逆向活性,reverse active mode) 。这电流启动右边 npn 晶体管基极 (base),通电至地,地和这枚npn集电极没有电位差,令输出端变为低压 (0 V) 。当 (A) 端电压变低,没有电流通往右边 npn 晶体管,地和这枚npn集电极之电位差为 5V,输出端转为高压。结果这单位就是一反相器 (图239)。

(图 239) 图238 之真值表

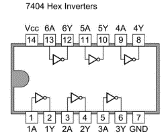

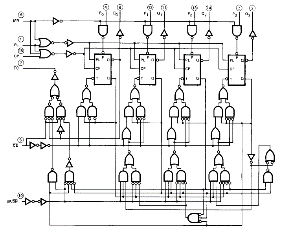

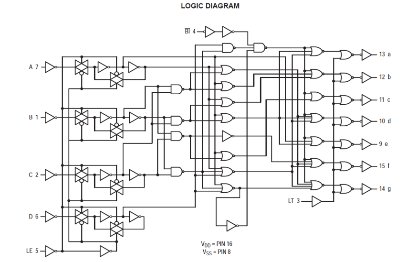

逻辑闸可以 是TT L 集成电路或 CMOS 集成电路,DIP 形式包装,用作数字电路电子零件。按线路接上各有关接点,完成设计之电路。一颗 DIP IC 内 (i) 有多个简易相同逻辑闸,不会只有单一逻辑闸。例如 TTL 7404 就内置六组 NOT 逻辑闸 (图 240) 。(ii) 多个复习而不同之逻辑闸如CMOS 4511 集成电路 (BCD to 7 segment) 内部结构则复杂得多 (图 272) 。

(图 240) 7404 接脚分布

(iv)互补式金属氧化物半导体 Complementary Metal-Oxide-Semiconduct

CMOS 是另一种消费者常用之集成电路的设计制程。在硅质晶圆模板上制出NMOS (n-type MOSFET)和 PMOS(p-type MOSFET)的基本组件 (图 241) ,由于 N MOS 与 PMOS 在物理特性上为互补性,因此被称为 CMOS。

(图 241) 一单位 CMOS 逻辑闸

CMOS 可用来制作静态随机存取内存 (RAM)、微控制器、微处理器、互补式金属氧化物半导体图像传感装置 (数码相机感光组件) 和其他数码逻辑电路系统。互补式金属氧化物半导体具有只有在晶体管需要切换启动与关闭时才需消耗能量的优点,因此非常节省电力且发热量少,且制作上也是最基础而最常用的半导体组件。CMOS 编号命名最常见的为 4xxx 系列

TTL 与 CMOS 分庭抗礼。两者相比较,TTL主要是速度快,CMOS 则是速度较慢但省电、成本比 TTL 低。随着制造 CMOS 工艺进步,其反应度已经超越 TTL。而且 CMOS 内部不具有制作麻烦的电阻,TTL 一段时期可说没有发展。目前 TTL 主要应用于教育或是较简单的数码电路。

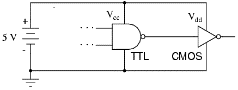

TTL 与 CMOS 电源电压,VDD或 Vcc,通常都是 5 V。但逻辑闸之1 (ON, 高压) 和 0 (OFF, 低压) 分辨电压不一样。两者之阈值 (threshold) 电压范围,即启动 CMOS 输出1 之输入电压和启动 CMOS 输出 0 之输入电压和TTL不相同,不兼容。在同样5V电源电压情况下,COMS电路可以直接驱动TTL,但TTL电路则不能直接驱动CMOS电路。

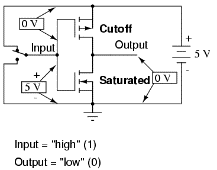

因此早期 TTL 和 CMOS 不可以如上图般接连。但后期随着新型品种 74HCxxxx (High speed CMOS) 和 74LS (Low power Schottky) 等推出市场,兼容问题基本上解决了。下图 (图 242) 简单解析 CMOS NOT 逻辑电子闸 (inverter) 如何运作。TTL 和 CMOS 工作原理可于网上选阅。

(图 242) CMOS Inverter电子逻辑闸运作

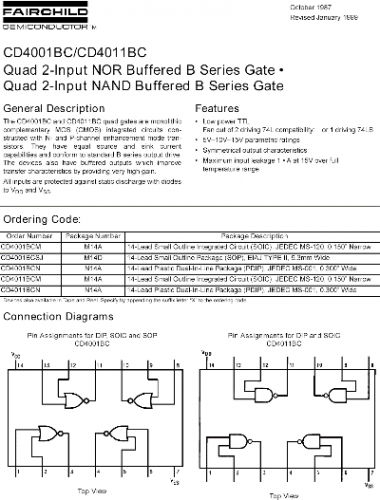

市面可购买之逻辑电子闸集成电路均有编号。零件规格特性每间提供货源之大厂,如早期之 FAIRCHILD 和现时之 MOTAROLA 或TEXAS INSTRUMENT (TI) 等皆印刷有关之手册。每间大厂都拥有有关每一产品网上之专页。

(图 243) CMOS编号 CD 4001和 CD 4011之描述和接脚

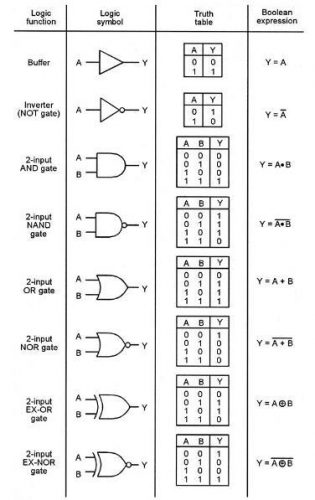

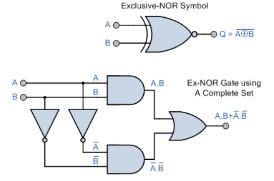

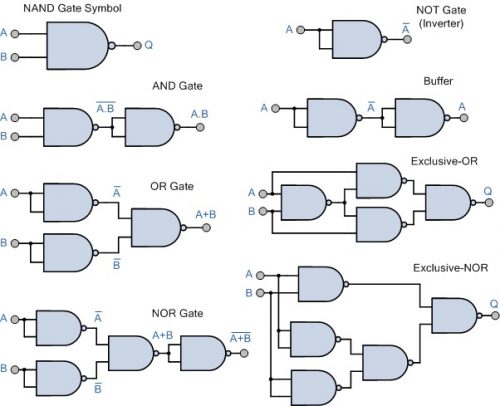

CMOS 依布尔代数逻辑组成不同电子逻辑闸去演绎7类二元布尔操作数AND、NAND、OR、NOR、XOR、XNOR 和 NOT (即 INVERTER)。

(图 244) 7种电子逻辑闸名称,符号和简介

其真值表如下 (图245) :

| INVERTER gate | |||||

|

(图 245) 七种电子逻辑闸之真值表

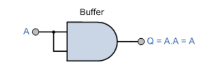

第七类电子闸不具逻辑运算,叫Buffer (缓冲器)。 0V 输入0V 输出 / 1V 输入1V 输出。作用是提高输入阻抗,尤其耦合Op – Amp IC。

电子逻辑闸符号和真值表总结:

(图 246) 各种电子逻辑闸符号和真值表

(v) 布尔表式和真值表

布尔表式 | 配合电子逻辑闸之真值表 |

A + B = A |  |

(图 247) 布尔表式 A+B = A 和相应之真值表

布尔表式 | 配合电子逻辑闸之真值表 |

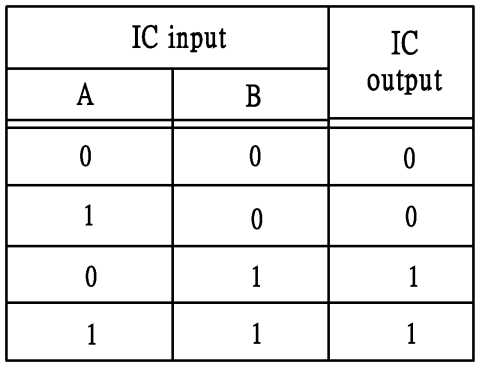

A + B = B |  |

(图 248) 布尔表式 A+B = B 和相应之真值表

(vi) 布尔代数逻辑,真值表和电子逻辑

STEM应用最深远和影响极大就是二元布尔代数操作数(binary Boolean algebraic expressions) 和电子逻辑闸数字计算 (logic gate digital computation) 互相之深度和复杂结合。完美体现STEM数学和科技于促进人类生活进步之伟大贡献。

(a) 双输入二进制元 (A B)

回顾最简单布尔表式 A+ B = A 和 A + B = B,适当逻辑闸组合可以把它们结合起来,即直接转数学为科技。以 4 个二进制位只有 22 ,即4 种变化,(0 0) 、(1 0) 、(0 1) 、 (1 1) 代表布尔方程 A + B = A 输入一单位电字逻辑闸 (即 AND、NAND、OR、NOR等) 不可以取得 (0 1 0 1) 答案。只能以二单位耦合电子逻辑闸 (OR加AND) 运作,如以下显示:

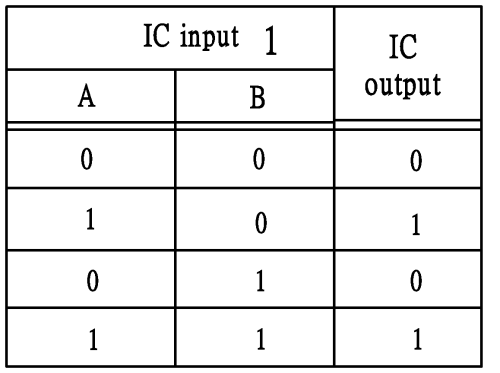

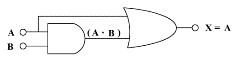

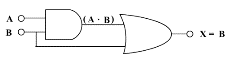

布尔表式 | 真值表 | 电子逻辑闸组合 (AND加OR) |

A + B = A |  |  |

布尔表式 | 真值表 | 电子逻辑闸组合 (AND 加 OR) |

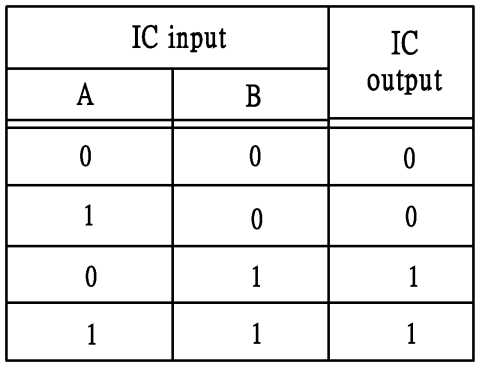

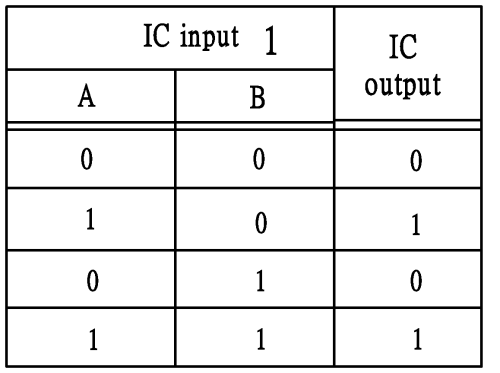

A + B = B |  |  |

用 (OR连AND) 组合一样可以:

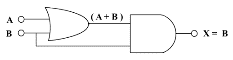

布尔表式 | 真值表 | 电子逻辑闸组合 (OR 加 AND) |

A + B = A |  |  |

布尔表式 | 真值表 | 电子逻辑闸组合 (OR 加 AND) |

A + B = B |  |  |

(1) 考虑一个不简易例子:

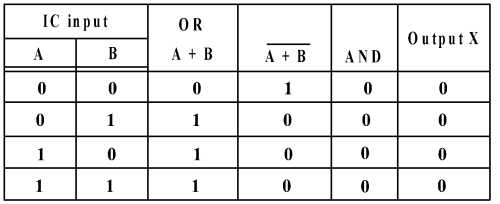

A + B = 总是低压 (i.e. 0)

很明显,只用 AND 加 OR 组合 或 OR加AND 组合不满足要求。我们尝试加一非门 (NOT gate) :

布尔表式 | 真值表 | 电子逻辑闸组合 (OR 加 NOT 加 AND) |

A + B = 0 |  |  |

或 NOR 加 AND |

(2) 再考虑:

A + B = 总是高压 (i.e. 1)

参考例子 (1),用NOR 加 NAND 便可以,自己试试。

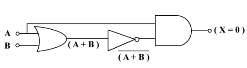

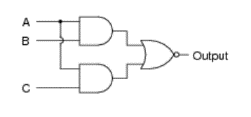

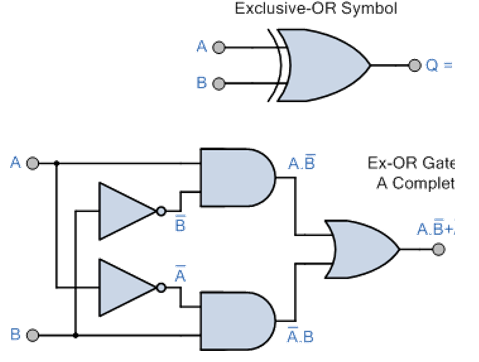

(b) 三输入二进制元 (A B C)

三输入二进制元如 (A + B + C) 有23 或 8 种二进制元变化,即 (0 0 0)、(0 0 1)、(0 1 0)、( 0 1 1)、(1 0 0)、(1 0 1)、(1 1 0) 和 (1 1 1)。考虑下图之逻辑组合:

尝试推算其二进布尔表达式。

(c) 独立和组合逻辑闸

先前陈述之7种二输入二进制元逻辑闸 (图 244, 245 和246) 每种不具必需性。每个逻辑闸既可独立运作,也可由其他逻辑闸组合而成。因此,我们可以验证基块逻辑闸组合成某个逻辑闸,从而产生所有二进制元数字布尔运算程序。

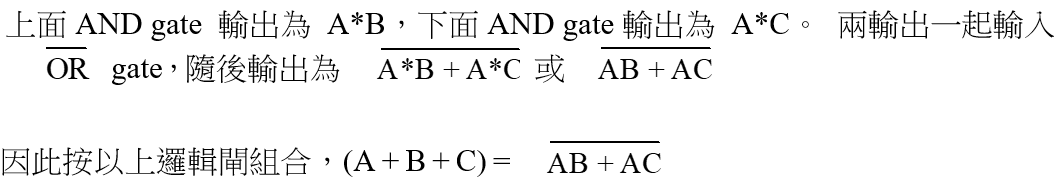

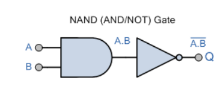

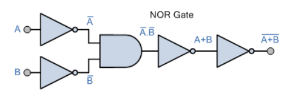

组合 (AND, OR and NOT) 称为全组合元。其他4个逻辑闸,即NAND、 NOR、 ExOR 和 ExNOR (包括 buffer),都可以由全组合元或其中两个构建而成,如下图所示:

|  |

|  |

用单一逻辑闸构建全部7 种逻辑闸称为基本元。NAND是基本元。只用 NAND 便可以构建全部7 种逻辑闸:

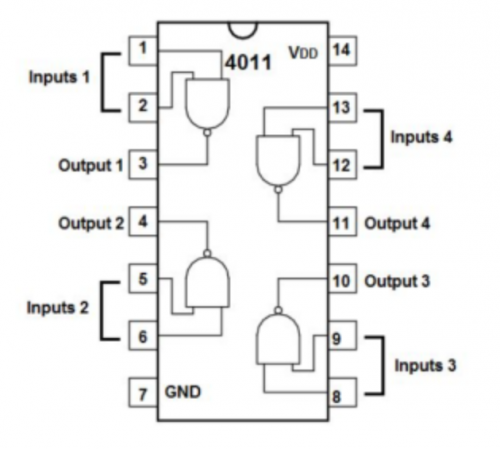

(d) 商 /民用逻辑闸芯片

CMOS 或 TTL 逻辑闸全部都以各类芯片出售,不用以晶体管或半导体亲手装组起来。 芯片垮国生产商如德州仪器 (TI)、摩托罗拉 (Motorola)、亚德诺半导体 (Analog Devices) 等经营多年,旗下生产民用芯片种类繁多,型号已标准化。个人计算机市场不断发展,所用芯片如中央处理器 (CPU) 、接口设置 (interface device) 等型号则不停更新。电子线路设计沿用多年之COMS 4xxx 逻辑闸芯片是不会被淘汰的。逻辑闸封装不只提供单一单位,全部封装都有多个或混合单位。下图显示各标准型号CMOS逻辑闸芯片:

CMOS IC | 描述 | CMOS IC | 描述 |

| 4081 | Quad 2-input AND | 4073 | Triple 3-input AND |

4011 | Quad 2-input NAND | 4023 | Triple 3-input NAND |

| 4071 | Quad 2-input OR | 4075 | Triple 3-input OR |

4001 | Quad 2-input NOR | 4025 | Triple 3-input NOR |

| 4070 | Quad Exclusive OR | 4082 | Dual 4-input AND |

4077 | Quad Exclusive NOR | 4012 | Dual 4-input NAND |

| 4000 | Dual 3-input NOR plus inverter | 4072 | Dual 4-input OR |

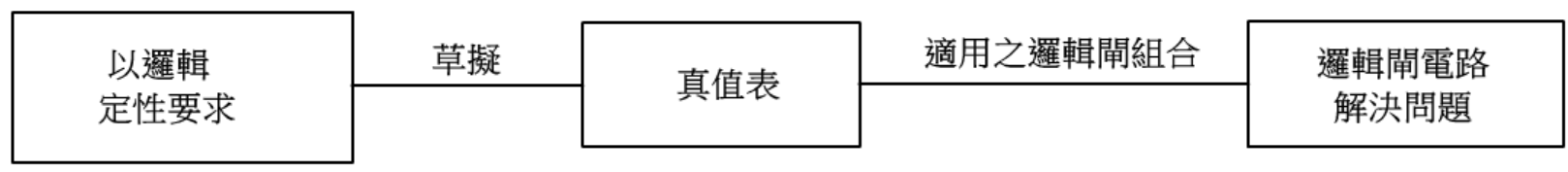

以上例子可见适当逻辑闸组合可以演绎基本布尔表式A + B = A 或 A + B = B。 事实上,最复杂计算机硬件电路之原始计算步骤就是决定二进 (0 1) 位状态之输出是 0 或是 1。简单地总结如下:

(e) 一个实用但相当复杂的四输入二进制元 (A B C D) 例子

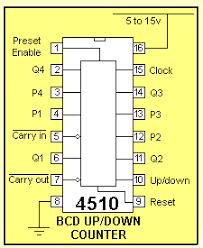

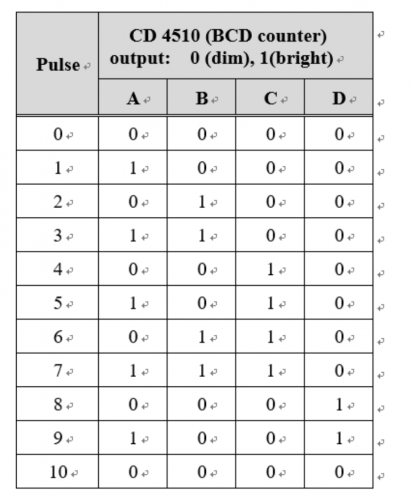

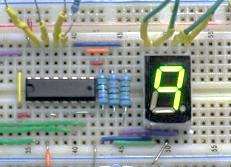

一个常见,但很复杂的例子便是硬件电路之BCD(二进制编码的十进制)计数器显示。下列三表格概述如何用四颗 LED 队列显示十进 0 至9 数字。电路涉及复杂软件式二元布尔逻辑运算。不过应极大供求需要,芯片厂商把整个复杂编程数字逻辑化,制成集成芯片推出市场。这就是以下介绍 IC CD 4510之起因。

要求 | 真值表 |

基于逻辑闸组合,设计一数字线路显示十进 0 至9 数字。 两颗二进制位LED 队列可显示22 或 4 种可能性,即0 至 4 数字,不达要求。 四颗二进制位LED 队列可显示24 或 16 种可能性,不独可以显示 0 至 9 数字,也可以显示其他字母和符号。这种数字名命叫十六进制。 要有一时钟,输出锁定频率方波脉冲讯号链。 二进制四位 (A B C D ) 真值表匹配十进数字输入,四位 (A B C D ) 输出。 |  |

逻辑闸线路 | ||

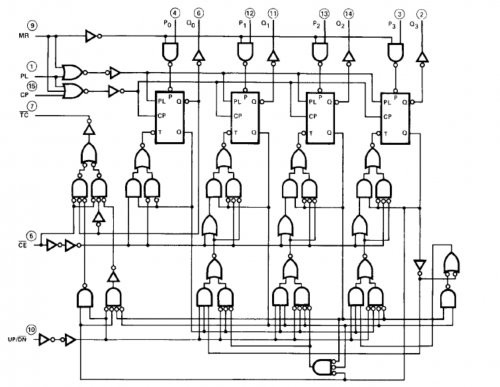

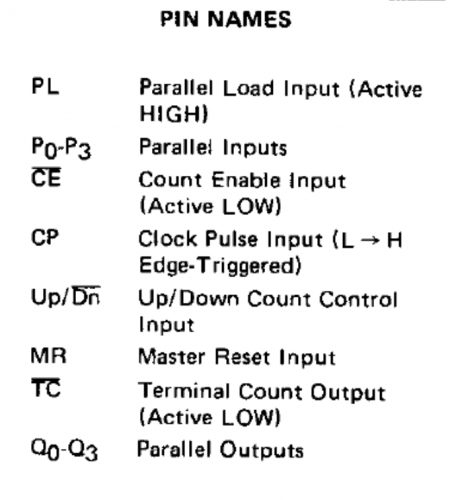

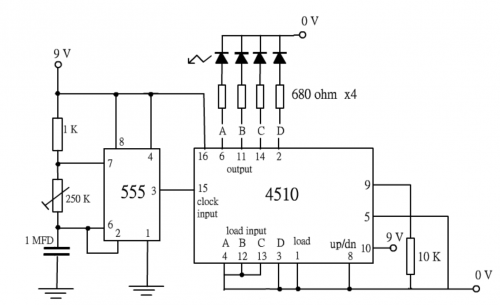

实现要求需要一复杂逻辑闸组合线路。 # 0显示为 (0 0 0 0 ),4颗LED队列显示为 (暗 暗 暗 暗), # 1显示为 (1 0 0 0 ),4颗LED队列显示为 (光 暗 暗 暗), # 2显示为 (0 1 0 0 ),4颗LED队列显示为 (暗 光 暗 暗) 如此类推。 适用之逻辑闸组合电路是市面有售之 BCD 4 bit计数器 IC CMOS CD 4510。其复杂内部结构如下图所示。 | ||

|  | |

CMOS CD 4510 BCD 4 bit计算器 | ||

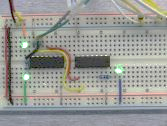

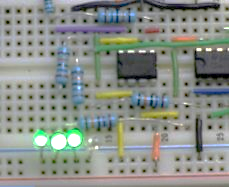

| CD 4510 IC计数器为一通用数字集成电路,接脚可接各种数字运算讯号。但目前工作只考虑输入脉冲方波 (时钟) 和输出4位 (A B C D 或 Q0 至Q3 ),因此第1、3、4、5、8、12和第13脚全部连接地。其他接脚,如第16脚 (VDD) 接 + 9V,第 9 脚 (重置) 通过 10K 电阻接地,第10脚接 + 9V,第 15脚接 555 IC无稳态复振器输出 (IC第 3脚) 约 3 Hz方波脉冲 (时钟) 。第 (2、6、11、14) 脚分别以4位 (A B C D ) 输出。下图显示于面包板接驳之线路。主题 9.3 (数字频率显示器) 有较详细闸述 CD 4510计数器功能。 | ||

|

| |

以下短片说明0 至9 数字如何由四颗 LED队列面包板上顺序显示。

CD 4510 BCD 4 bit output

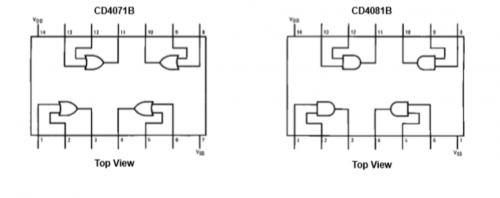

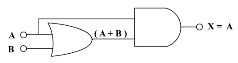

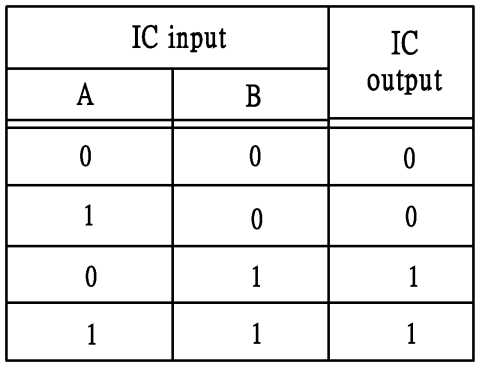

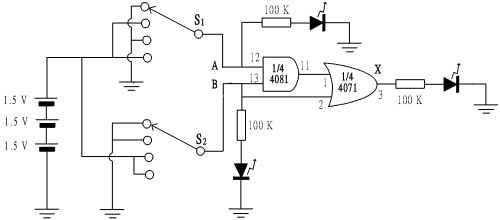

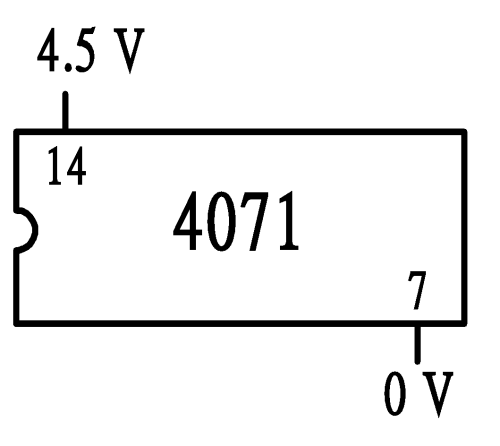

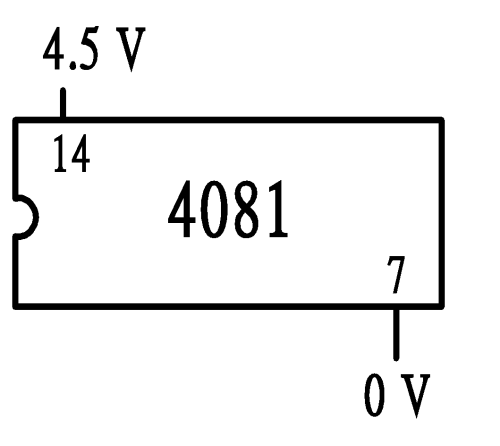

习作 (11 ) :设计以 CMOS CD 4071 (Quad 2-input OR gate,四2输入端或门) 和 CD 4081 (Quad 2-input AND gate,四2输入端和门) 逻辑闸数字电路验证布尔表式 A + B = B

物料:CD 4071, CD 4081, 面包板,4.5 V 电源,LED,100 K 电阻 (若要LED) 亮些,可降低阻值,如 50 K),接线,三刀四掷选择器。

|

步骤:

(1) 按下图线路完成接驳。

|  |

|

(图 249) 布尔表式 A+B = B 和相应之电子闸电路

(2) 转动三刀四掷选择器旋钮令 (A, B) 按 (0 0),(0 1),(1 0) 和 (1 1) 变化。观察输入端A,B和 输出端 X LED亮度。

|  |  | ||||||

线路实物图 | 三刀四掷选择器(只用其中两组) |

|

|  |  |

|

|

| ||||||||||||||||||

(图 250) A 和 B 端连续输入 (0 0),(1 0),(0 1) 和 (1 1) 显示 X 输出端

A + B = B

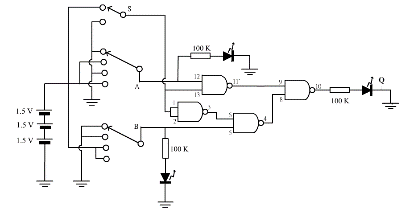

何时选择数字讯号以 A + B = A 运算,何时选择数字讯号以 A + B = B 运算?这方面需要数据选择器 (multiplexer)。数据选择器逻辑电路之真值表为

S | A | B | Q | |

0 | 0 | 0 | 0 | A + B = A |

| 0 | 0 | 1 | 0 | |

0 | 1 | 0 | 1 | |

| 0 | 1 | 1 | 1 | |

1 | 0 | 0 | 0 | A + B = B |

| 1 | 0 | 1 | 1 | |

1 | 1 | 0 | 0 | |

| 1 | 1 | 1 | 1 | |

当 S 为 0 时,数字讯号 A和 B 输入以 A + B = A 运算,结果 Q = A。当 S为 1 时,数字讯号 A 和 B 输入以 A+ B = B 运算,结果 Q = B。以上可看成是 A+ B = A 或 A+ B = B 运算之扩张真值表。可以说是数字电路理论香农展开 (Shannon’s expansion) 于 2 选 1 数据选择器之最简化演绎。

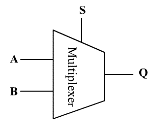

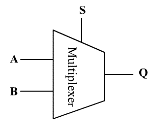

数据选择器有自身符号 (图 251)。2 选 1 电子选择器可比喻为一手动单刀双掷选择器 (图 252)。这类集成电路也称三态逻辑闸。

|  |

| ||||||||

2 选 1 电子选择器 | 比喻为一手动单刀双掷选择器 | 香农展开真值表 |

(图 251) (图 252)

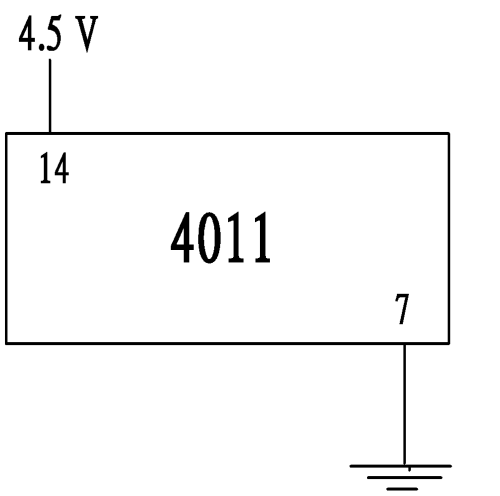

习作 (12):设计以 CMOS CD 4011 (Quad 2-input NAND gate,四2输入端与非门) 逻辑闸数字电路模拟布林表式 A+ B = A 或 A + B = B 2 选 1

|  | |||||||||||||||||||||||||||||||||||||||

物料: CD 4011,面包板,4.5V 电源,LED,100 K 电阻 (若要 LED 亮些,可降低阻值,50 K),接线,三刀四掷选择器,单刀二掷选择器

步骤:

(1) 按下图线路完成接驳。

|  |

| |

(图 253) A + B = A 或 A + B = B 2 选 1 线路 |

(2) 转动单刀二掷选择器旋钮 S 令 IC 第 13 脚接 0V,即 S = 0。。

(3) 转动三刀四掷选择器旋钮。

(4) 选 (A B) 为 (0 0) ,记录 LED Q 亮度。

(5) 选 (A B) 为 (1 0) ,记录 LED Q 亮度。

(6) 选 (A B) 为 (0 1) ,记录 LED Q 亮度。

(7) 选 (A B) 为 (1 1) ,记录 LED Q 亮度。

(8) 调校 S 接 4.5 V,即 S = 1。重复以上步骤。

结果:完成下表

S | A | B | LED Q亮度 (光 = 1,暗 = 0) | |

| 0 | 0 | 0 | A + B = ( ) | |

0 | 1 | 0 | ||

| 0 | 0 | 1 | ||

0 | 1 | 1 | ||

| 1 | 0 | 0 | A + B = ( ) | |

| 1 | 1 | 0 | ||

| 1 | 0 | 1 | ||

1 | 1 | 1 | ||

(vii) 频率计数器 (Frequency counter)

实用计算机数字电路当然不会使用手动选择器来转换众多执行指令。任务交予数据选择器和时钟。习作 (12) 只是一个模拟数据选择器运作线路,真实数据选择器应用则复杂得多 (网上自修) 。数据选择器需要外接时钟产生一连串开 ((1), 5V)/关 ((0), 0V) 脉冲讯号链始可运作。时钟提供时基作数字运算,时钟通常指计数器 (frequency counter)。计算机硬件计数器采用晶体压电效应物料 (piezo electric material),例如石英 (quartz) 产生精准振荡方波脉冲讯号链,可达至10-9 秒分辨准确度。时钟越快,准确度越高。一般用途振荡频率幅度为数Hz至 数千 Hz,用不着使用石英振荡。运算放大器耦合RC电路作无稳态复振器 (弛张振荡器) 、CMOS反相逻辑闸耦合电容起振器或是专门为振荡而设计之IC如555都非常合适。

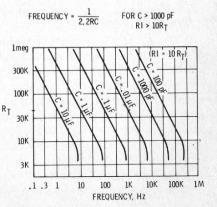

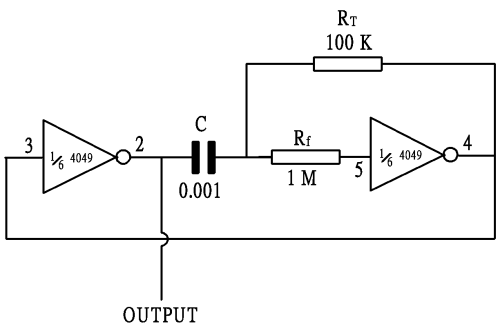

Op-Amp 弛张振荡电路 (图 228) 为广泛采用之无稳态复振电路,主题 8.3 已有所讨论。CMOS 无稳态复振电路有多款,下图 (图 254) 以 CD 4049 反相逻辑闸 IC 起振之方波频率为 f = 1/2.2 RC。当 R = 100,000 W 和C = 0.001 x 10-6 F,

f = 1/(2.2 x 100,000 x 0.001 x 10-6) Hz 或 4545 Hz。

若考虑计算误差、电阻阻值和电容数值误差,可接受之实值为计算值 (+/-) 15 %,上述例子则为 4545 (+/-) 682 Hz

|

(图 254) CD 4049 反相器 IC 起振器

|

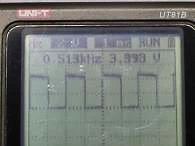

(图 255) CD 4049 起振器产生5130 Hz方波 |

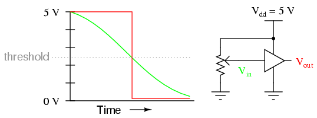

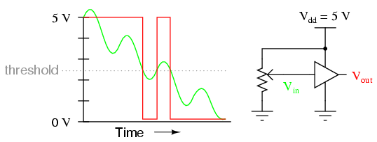

(viii) 失真模拟讯号数字化

讯号数字化一个主要用途是消除和讯号一起的噪声 。当没有噪声模拟波动电压输入电子逻辑闸反反相器 (即输入 0 输出也是 0, 输入 1 输出也是 1,也称缓冲器,buffer) 默认一阈值电压,便可转换为 (0 1) 位。下图 (图 256) 可见若输入模拟讯号电压高于阈值电压,数字讯号输出保持于高压,即 +5V或 (1) 。 当输入模拟讯号电压低于阈值电压,数字讯号输出实时变为低压,即 0 V或 (0) , 并保持于这数值。(红线为数字讯号电压,绿色曲线为波动之没有噪声模拟讯号电压)。

(图 256) 模拟/数字转换阈值电压

若模拟讯号有噪声,(0 1) 数字讯号位将会不一样。如果把缓慢改变迭有杂讯之DC 模拟讯号 (绿色),即失真模拟讯号,转换为数字讯号 (红色),阈值电压会有三交叉点而不是只有一交叉点,结果有两个数字脉冲而不是只有一个 (图 257)。

图 257) 阈值电压出现三次,缓冲器数字讯号输出不一样

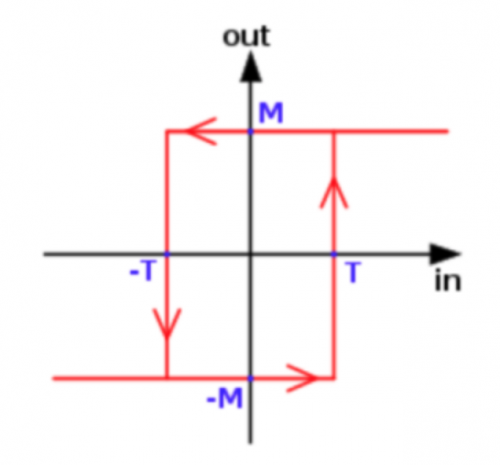

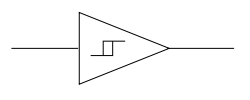

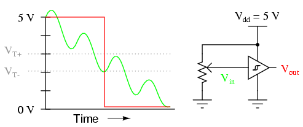

解决方法是用一类电路叫施密特触发器 (Schmitt trigger),整个线路以下图为符号:

上图正中图案代表迟滞现象 (hysteresis),用来显示铁磁物料之 B-H 磁滞曲线。施密特触发器之组合为一运算放大器接驳成比较器及在非反相输入端作正回馈并设下两阈值电压,一高一低。由低阈值电压和高阈值电压激发之数字位 (0) 和 (1) 及期间之时差都决定于模拟讯号之变化。这种往返机制跟迟滞现象很相似。

(图 258) 失真模拟讯号用施密特触发器数字化后呈正常脉冲

考虑图 258,当模拟电压高于高阈值电压,数字位 (1) 态被启动,输出维持于 +5V。若模拟讯号电压下降至低阈值电压,数字位输出实时变为 (0) 态,即0V,并保持此值至另一变化。换句话说,高阈值电压至低阈值电压期间,数字位保持于 (1) 态。结果是数字脉冲输出只有一方波而不是两方波 (图257)。

施密特触发器示意图 (图 259). OX 和OY 轴分别为输入和输出电压。 T 和 −T 为转换阈值电压,M 和 −M 为输出数字电压。当输入电压 (T) 高于高阈值电压,输出数字电压为 +5V (M) 并维持此值。若输入电压下降至低阈值电压 (-T),输出数字电压实时变为0V (-M),并维持此值。重复此模式出现如一B-H 磁滞曲线 (图 259)。 |

(图 259) 施密特触发器转换曲线 | |||

读者若想了解施密特触发器详细资料,可上网页阅览。

9.2 硬件、软件、二进制位,字节、数字运算和个人计算机 (PC)

(i) 硬件与二进制数字运算

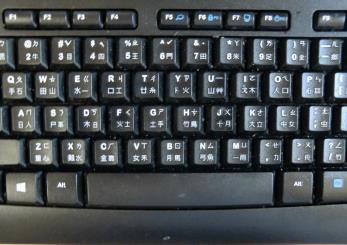

计算机硬件为一套有物理形状、可触摸、复杂的电子和机械设备,包括机壳、中央处理器 (CPU)、显示器、键盘、储存器、graphics 卡、sound卡、扬声器和主板 (motherboard)。计算机硬件运作需要启动内置操作系统 (operating system, OS) 和输入一组有数字逻辑的二进制字节指令,即软件。

二进1 位 (1 bit) 有 21 即 2 种变化 0 和 1,实际电子用途只可以说是一个开关制处于接通 (即 1) 和关 (即 0) 状况。二进2 位 (2 bit) 有 22 ,即 4 种二进制变化 (0 0),(0 1),(1 0) 和 (1 1)。实际电子用途只是作为二进制 (binary bit) 位,广泛地用于各系列电子计算器 (计算机) 数字运算。二进3 位 (3 bit) 有23,即 8 种二进制变化 (0 0 0)、(0 0 1)、(0 1 0)、( 0 1 1)、(1 0 0)、(1 0 1)、(1 1 0) 和 (1 1 1)。实际电子用途不如2位普遍。近年有学者尝试用二进3位把易经之乾坤八卦和六十四卦作电子运算演绎 (可上网搜寻,也可想象占卜龟壳内之三枚铜钱,代表天、地、人),超越数字、图形和符号范畴。二进4 位 (4 bit) 有 24 ,即16 种二进制变化。实际电子用途是作为十六进制 (hexadecimal) 和键盘符号普遍采用的拉丁语系ASCII (American Standard Code for Information Interchange) 制式之标准。

第一代数字计算概念源于二进制4 bit 位。 4 bit 位可如下表 (图260) 分配二进、十进和十六进制进行运算。

Display | |||

Binary | Octal | Decimal | Hexadecimal |

| 0000 | 0 | 0 | 0 |

0001 | 1 | 1 | 1 |

| 0010 | 2 | 2 | 2 |

0011 | 3 | 3 | 3 |

| 0100 | 4 | 4 | 4 |

0101 | 5 | 5 | 5 |

| 0110 | 6 | 6 | 6 |

0111 | 7 | 7 | 7 |

| 1000 | 10 | 8 | 8 |

1001 | 11 | 9 | 9 |

| 1010 | 12 | 10 | A |

1011 | 13 | 11 | B |

| 1100 | 14 | 12 | C |

1101 | 15 | 13 | D |

1110 | 16 | 14 | E |

| 1111 | 17 | 15 | F |

(图 260) 4-bit字节和各进位采用之显示

二进制 4 bit 电子运作不可以语言化,即不足以分配十进制阿拉伯数目字 0 至 10,英文 26 个字母 A 至 Z 和其他常用之符号。二进制8 bit有 28 即 256 种变化,可分配十进数字 0 至 10,英文 26 个字母 A 至 Z 和常用显示之符号如 =、>、<、/、@ 等之 ASCII 字符集 (图 261, 262)。指令计算机硬件运作需要程序语言编写程序,即软件。

机器可以译码以二进制4 bit编写之程序,但它不可以按人类语言规范作指令运算。换句话说,这类初阶程序编写很有局限性,不可以以人类语言编写,故称之为「机械语言」(machine language)。以二进制8 bit,或1字节编写之程序基本上可认识人类常用之语言字汇为指令规范,衍生初期极为普及之BASIC,FORTRAN等程序。

(图 261) 盘主板之ASCII字符符号

ASCII 的局限性在于只能显示 26 个基本拉丁字母、阿拉伯数目字和英式标点符号,因此只能用于显示现代英语或美式英语。后来发展了「统一码」(Unicode),可用于其他语系。ASCII字符集普遍地用于键入程序编写,其简易 user-Friendly 程度很为人们接。(网上键入关键词 (ASCII)可得较详细资料)

Binary | Decimal | Hexa decimal | Graphic | Binary | Decimal | Hexa decimal | Graphic | Binary | Decimal | Hexa decimal | Graphic |

0010 0000 | 32 | 20 | (space) | 0100 0000 | 64 | 40 | @ | 0110 0000 | 96 | 60 | ` |

| 0010 0001 | 33 | 21 | ! | 0100 0001 | 65 | 41 | A | 0110 0001 | 97 | 61 | |

0010 0010 | 34 | 22 | “ | 0100 0010 | 66 | 42 | B | 0110 0010 | 98 | 62 | b |

| 0010 0011 | 35 | 23 | # | 0100 0011 | 67 | 43 | C | 0110 0011 | 99 | 63 | |

0010 0100 | 36 | 24 | $ | 0100 0100 | 68 | 44 | D | 0110 0100 | 100 | 64 | d |

| 0010 0101 | 37 | 25 | % | 0100 0101 | 69 | 45 | E | 0110 0101 | 101 | 65 | |

0010 0110 | 38 | 26 | & | 0100 0110 | 70 | 46 | F | 0110 0110 | 102 | 66 | F |

| 0010 0111 | 39 | 27 | ‘ | 0100 0111 | 71 | 47 | G | 0110 0111 | 103 | 67 | g |

0010 1000 | 40 | 28 | ( | 0100 1000 | 72 | 48 | H | 0110 1000 | 104 | 68 | h |

| 0010 1001 | 41 | 29 | ) | 0100 1001 | 73 | 49 | I | 0110 1001 | 105 | 69 | |

0010 1010 | 42 | 2A | * | 0100 1010 | 74 | 4A | J | 0110 1010 | 6A | ||

0010 1011 | 43 | 2B | + | 0100 1011 | 75 | 4B | K | 0110 1011 | 107 | 6B | k |

| 0010 1100 | 44 | 2C | , | 0100 1100 | 76 | 4C | L | 0110 1100 | 108 | 6C | |

0010 1101 | 45 | 2D | – | 0100 1101 | 77 | 4D | M | 0110 1101 | 109 | 6D | m |

| 0010 1110 | 46 | 2E | . | 0100 1110 | 78 | 4E | N | 0110 1110 | 110 | 6E | |

0010 1111 | 47 | 2F | / | 0100 1111 | 79 | 4F | O | 0110 1111 | 111 | 6F | o |

| 0011 0000 | 48 | 30 | 0 | 0101 0000 | 80 | 50 | P | 0111 0000 | 112 | 70 | |

0011 0001 | 49 | 31 | 1 | 0101 0001 | 81 | 51 | Q | 0111 0001 | 113 | 71 | q |

| 0011 0010 | 50 | 32 | 2 | 0101 0010 | 82 | 52 | R | 0111 0010 | 114 | 72 | |

0011 0011 | 51 | 33 | 3 | 0101 0011 | 83 | 53 | S | 0111 0011 | 115 | 73 | s |

| 0011 0100 | 52 | 34 | 4 | 0101 0100 | 84 | 54 | T | 0111 0100 | 116 | 74 | |

0011 0101 | 53 | 35 | 5 | 0101 0101 | 85 | 55 | U | 0111 0101 | 117 | 75 | u |

| 0011 0110 | 54 | 36 | 6 | 0101 0110 | 86 | 56 | V | 0111 0110 | 118 | 76 | |

0011 0111 | 55 | 37 | 7 | 0101 0111 | 87 | 57 | W | 0111 0111 | 119 | 77 | w |

| 0011 1000 | 56 | 38 | 8 | 0101 1000 | 88 | 58 | X | 0111 1000 | 120 | 78 | |

0011 1001 | 57 | 39 | 9 | 0101 1001 | 89 | 59 | Y | 0111 1001 | 121 | 79 | y |

| 0011 1010 | 58 | 3A | : | 0101 1010 | 90 | 5A | Z | 0111 1010 | 122 | 7A | |

0011 1011 | 59 | 3B | ; | 0101 1011 | 91 | 5B | [ | 0111 1011 | 123 | 7B | { |

0011 1100 | 60 | 3C | < | 0101 1100 | 92 | 5C | \ | 0111 1100 | 124 | 7C | | |

| 0011 1101 | 61 | 3D | = | 0101 1101 | 93 | 5D | ] | 0111 1101 | 125 | 7D | |

0011 1110 | 62 | 3E | > | 0101 1110 | 94 | 5E | ^ | 0111 1110 | 126 | 7E | ~ |

| 0011 1111 | 63 | 3F | ? | 0101 1111 | 95 | 5F | _ |

(图 262) ASCII字符符号

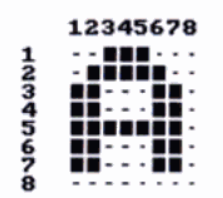

当我们按下计算机键盘其中一键时 (俗称单击),若采用10-bit字符架构,键盘实时输出一start bit (low),跟着一8 bit 数据位, 一stop bit (high)。例如单击A键,屏幕见「A」字。按 (图 262, ASCII 字符符号) 所示,输入二进制数据字节为 (0100 0001)。计算机运算 (0100 0001) 字节,光栅扫描 (Raster scan) 并以8 x 8 像素格栅矩阵图形屏幕显示「A」(图 263)。可见一简单动作其实已经进行了一连串复杂执行指令。键盘运作机理就是用一种user-friendly和简单方法达至与计算机互动。

|

Character “A” in 8x 8 Matrix by Raster scan |

(图 263) (0100 0001) 位元组屏幕矩阵图形显示为「A」

(ii) 程序语言与软件

(a) 民用和商业软件

程序语言(programming language),是用来定义计算机程序的形式语言。它是一种被标准化的交流技巧,用来向计算机发出指令。计算机语言让程序设计师能够准确地定义计算机所需要使用的数据,并精确地定义在不同情况下所应当采取的行动,不可以有丝毫错误。程序语言有低阶和高阶之分,发展也有先后。低级语言指令普通人解不通,只供机械认识,因此叫机械语言 (machine language)。高级语言以人类的日常语言为基础的一种程序语言,使用一般人易于接受的文字来表示,以方便对计算机认知较浅的人亦可以大概明白其内容。

高级语言指令早于上世纪50年代已开发,其后流行使用的先有数学科应用之FORTRAN (FORmula TRANslator)、商业用的 COBOL (COmmon Business Oriented Language) 、通用之BASIC (Beginner’s All-purpose Symbolic Instruction Code) 和办公室用之LOTUS – 123 电子表格等软件 (spreadsheet)。电子表格之应用是与计算机互动,功能以表格形式组织、分析和储存数据。以上程序语言早期只供大型计算机 (mainframe) 使用。后来因个人计算机 (PC,personal computer) 开发,中央处理器 (CPU) 广泛应用及运作速度飞跃发展,程序语言变得日新月异。现时最受欢迎之程序语言有Java、C#、Python、Ruby 等。

软件是一系列按照选用程序语言和特定顺序组织的计算机数据编程和指令,是计算机中的非有形部分。硬件之核心组件中央处理器 (CPU),发展飞跃,而配合之软件和操作系统也日新月异。上世纪70年代初期个人计算机操作系统 (Operation System, OS) 全部使用 DOS (Disk Operating System) 当时流行之英文文书软件有 「WordStar」 和 「Word Perfect」。 因 DOS 指令不浅白,并不user-friendly,所以后来被以桌面档页图标 (icon) 和鼠标 (mouse) 为卖点操作简易之微软「窗口」(Windows) OS全面取代。编写多个最初版本「窗口」之程序语言为Visual Basic 和 Visual Basic. NET。最新「窗口 10」 版本 OS则用C作基础,后来加入更高阶程序语言如C#、CPP 或 Pytho。微软著名软件为文书用经常更新之捆绑式 「Office」,初期版本内有文书用之 「Word」、 电子表格 「Excel」、 演讲显示用之 「PowerPoint」 和 电邮用之「Outlook」。后来加入「OneNote」、 「OneDrive」和视像传输用之「Skype」。

(b) 工业软件

广泛地说,处理工程、矿业、化工、能源等范畴制造业讯息之软件谓之工业软件。工业软件可处理评估、职业成本、制作之会计,经营或安排、专业物料设计,生产程序解决方法等。

MATLAB 捆绑Simulink 是工程界广用之软件 。MathWorks 开发MATLAB (“matrix laboratory”) 。软件具多功能性质,可作矩阵运算、图解函数和数据、实施算法、创建用者接口与其他编写程序链接。至 2020年,全球有多于 400 万用家。MATLAB用户具工程、科学和经济等专业经验。大有名堂之 AutoCad、CorelRAW、Photoshop 软件已广受设计艺术家欢迎数十载。

(c) 移动智能手机软件应用 (Apps, Software Applications)

步入千禧年代,互联网应用极之普及。智能手机已是个人日常之必需品。目前智能手机软件 (或称 Apps) 之操作系统源码不是iOS就是Android,但都需要使用移动程序语言。不像桌上计算机「窗口 10」OS程序语言主要有 C,C++ 和C#,流动电话之移动程序语言有多款,包括Java、 Javascript、 C#、 C++、 Python、 PHP 等,全部支持Internet Explorer (IE), Google, Chrome和Firefox 浏览器。

(d) 「云端」运算

「云端」为一比喻词,没有实质意思,可理解为超区域运作,如浮云一样。「云端」运算近年兴起,但不视作一发明产业。「云端」服务指透过互联网提供各类承索服务,或「一经要求,即可使用」之服务设施。「云端」计算机系统资源储存于大型遥远数据库,不需用者自行管理。不论以太网络 (ethernet) 桌上计算机或是其他接收速度和内存足够之移动电子装置,只要能上互联网,都可以如下图般接触 「云端」服务。

主要「云端」服务有:

* 电邮收发

* 数据储存、备份、数据检索

* 编写和检测 Apps

* 影音串流 (Audio and video streaming)

* 提供软件

广义地说,有三类「云端」服务: (i)「软件即服务」(Software-as-a-service, SaaS) ,(ii)「基础设施即服务」(Infrastructure-as-a-service, IaaS) 和 (iii)「平台即服务」(Platform-as-a-service, PaaS) 。SaaS 有销售授权用家自行网上安装软件如微软「Office 2016」和「Office 365」,有别于传统 CD-ROM 微软Office软件。IaaS有自行选择服务器, PaaS 则可寻找自我宣传之网页设计平台。

「云端」服务甪者可由Dropbox或Google Drive在不同计算机检视、发放或储存电邮。时下流行手机拍摄后Instagram上「云端」储存或检索。「云端」之高流动性尤其适用于人工智能应用,例如物联网 (IoT) 、无人驾驶、无人机、机械人等。

免费网上电邮服务如 Gmail、Yahoo mail和Hotmail 由浏览器提供,有别于「云端」服务。

(iii) 二进制字节架构跳跃式发展

虽然 8 bit字节程序数字字句可转换为键盘 ASCII字符输入,但8 bit字节是中央处理器基本上可以处理之数字字节,远远达不到 CPU 运作速度随时间增加而作对数式倍增之要求。因此 2 字节 (16-bit)、4 字节 (32-bit) 和现时起步之8 字节 (64-bit) 数字字句程序相继出现。相关之程序语言也变得五花八门。读者可再参阅网页得较详尽之有关资料。

总结数字电子之开拓和发展,证明数学 (布尔代数学) 和科技有唇齿相依不可分离关系。数字电子应用之深度广泛就是 STEM空前成功的一个极好例子。

9.3软件和硬件正向/逆向工程 (基于网上资料)

(i) 软件正向/逆向工程

顾名思义,正向工程是由原料至产品的工序。逆向工程则是另一种技术过程,即对一项目产品进行逆向分解,分析及研究。从而演绎并得出该产品的处理流程、组织结构、功能效能规格等设计要素,以制作出功能完全一样的产品,或进一步提升该产品效能。

软件原始码 (source code), 指令 (instruction), 编译代码 (compiled code) 和 二进目标代码 (binary object code)

软件和硬件一定要精准耦合才可使一台电子计算器正常运作。以外行人而言,就是软件命令硬件何时和如何工作。要一窥全豹,可从软件起始一步一步技术性地跟进,到硬件落实执行。这过程称软件正向工程。.

计算器正向工程由决定采用某一程序语言开始,跟着配合计算机 OS编写一没有错误之程序。举例用C语言编写屏幕显示方程式 3 + 8 = 11 如下:

| Line | |

| 1 | #include |

| 2 | |

| 3 | int main() |

| 4 | { |

| 5 | int a, b, c; |

| 6 | a = 3; |

| 7 | b = 8; |

| 8 | c = a + b; |

| 9 | printf(“%d + %d = %d\n”, a, b, c); |

| 10 | return 0; |

| 11 | } |

头文件 (standard input output as header) 为C 语言指令,理解为从键盘标准输入并以屏幕标准输出。第三行int main() 宣示主要功能。这些全部指令称作原始码 「source code」。计算机硬件主体不识辨别C 语言或其他高级语言编写之程序,只接受0 (0V) 或1 (5V)之二进制比特脉冲讯号。有需要用一编译程序 (complier) 把高级语言转为低级语言如汇编语言 (汇编语言,assembly language)、目标代码 (object code) 或二进制机械语言 (binary machine language),产生令硬件可执行之程序。整体结果是把一大堆0 和1二进制比特以字节 (字节,byte) 或 字组 (word) 精准地和非常有条理地汇入硬件各组件输入端口,进行繁复电子逻辑闸运算。

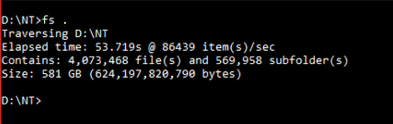

如想修改程序显示5 + 7 = 12,只要改a为5,b为7便可以了。若遗失了原始码,便要从新辨清用可种语言,重组编写或优化程序。这就是软件逆向工程。不过复杂软件程序之原始码如 「窗口10」 可以有逾400 万档案 和500 GB 字节 (图264)。若不提供原始码,程序专家们肯定不知于程序那处作适当修改。

(图264) 「窗口 10」档案大小

若需要修改原始码失掉之软件程序便要进行逆向工程步骤。软件逆向工程涉及基于二进制机械语言逆向改写为程序之原始码。改良或恢复编写程序便需要获取其原始码。一则可以修正程序错误,二则可以辨认恶意植入之程序病毒。软件程序逆向工程目的若为抄袭或复制便产生侵犯版权问题。软件程序逆向工程不仅极为复杂,也化大量金钱而通常得不偿失。

(ii) 硬件正向/逆向工程

芯片 (IC) 和系统单芯片 (SoC,System-on-a Chip) 制作产业

广义地说,硬件逆向工程是把一件计算机设备折散,理解它是如何运作。举个例子:有厂商想要知道竞争对手之中央处理器如何运作,便购买了一台,完全折散它,跟着造一款一模一样之CPU。不过这行为大部份国家都视作非法。事实上硬件逆向工程不仅化钱,更需要专门技术。为什么不直接向代理商购买?

芯片组产业正向工程大致可分为两类:(i) 整合组件制造 (IDM,Integrated Design and Manufacture) (ii) 代工生产 (OEM,Origional Equipment Manufacture) 。

(1) 整合组件制造 (IDM)

英文缩写 IDM要点放在字母 M,即制造,设计和其他工序不可以制造产品。整合组件制造一词解作厂商把 IC之设计、芯片制造、包装和测试集于一身,全部自家承办。当半导体IC产业还处于不十分先进年代,整合组件制造是那时普遍采用之工序。传统IC品牌 Intel 公司之桌上计算机 「Intel CPU」 便是IDM行业例子之表表者。

现时智能手机当道,每人都一机在手,令 Intel 或其他桌上计算机IDM厂家只可以分享广大电子市场一小份额,绝大份额都给生产智能手机内置之先进及复杂芯片组厂家占据了。基于生态系统环境及成本效益诱因,智能手机芯片组厂家不会采用IDM工序生产极之精准及超小型主芯片组。分工合作生产优胜过一家承办。智能手机主芯片组分别由 (i) 软件辅助芯片电路设计、 (ii) 光刻、(iii) 蚀刻、(iv) 硅晶圆片生产、(v) 包装和 (vi) 测试不同厂家承办。生产一环,即工序 (ii) 至 (iv) 叫代工生产 (OME) ,是整个产业主要环节。

(2) 代工生产 (OEM)

(a) EUV 光刻蚀和代工生产

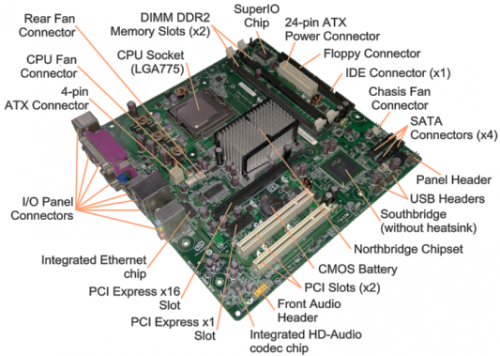

桌上计算机主板机安放了CPU,graphic card, RAM 槽等等 (图265)。但智能手机不可以承受如此空间奢侈。主芯片组 (chipset) 一定要包括主要线路组成并要造得非常细小。智能手机之「脑」, 即系统单芯片 (SoC chipset,System-on-a-Chip),便是厂家把各主要组成如 CPU,GPU,内存,通用串行总线控制器 (USB controller),电源管理组,无线接收组如 WiFi、 3G、 4G LTE、5G、蓝牙等等一体化地刻在一细小硅芯片上 (图266)。

|  |

(图265) 桌上计算机主板机布局 | (图266) A smartphone SoC chipset (Kirin 970) |

怎样才可以生产如此精密之系统单芯片?首先交由电路设计工程师完成芯片设计 (需要软件辅助) 。跟着涉及两层次工序:(i) 纳米级 (nm, 即 10-9 m) 光刻蚀和 (ii) 代工生产 (OEM,Original Equipment Manufacture) 嵌入各组件制成晶圆片。现今世界上只有一家「公司」有能力制造极高工艺水平之EUV (Extreme Ultraviolet,13.3 – 13.7 nm 电磁波段) 光刻机 (图267),于2019年已达致 7 nm 光刻规格。 下列流程简介EUV光刻蚀工艺程序:

|  |  |  | |||

(i) Preparation of wafer | (ii) Application of photoresist | (iii) Alignment of photomask | (iv) Exposure to EUV |

|  |  | ||

(v) Development and removal of photoresist exposed to EUV | (vi) Etching of exposed oxide | (vii) Removal of remaining photoresist |

按芯片组设计复杂程度,重复步骤 (iii) 至 (vi) 。

这家独占鳌头EUV光刻机制造商总部在荷兰,叫ASML (Advanced Semiconductor Materials International) Holding of the Netherlands. 事实上这家由数大垮国企业提供技术支持,用家财力支持之「公司」只销售技术,售卖光刻机,不造芯片组制成品。制造商和用家一起成为持份者。

(图 267) 制造 7 nm 系统单芯片开拓者,一台ASML EUV 光刻机

在2019年,除了装运到三星和英特尔,一半ASML输出之26台EUV光刻机都去了台积电 (TSMC, Taiwan Semiconductor Manufacturing Company Ltd.) 为各大手机生产商做代工 (OEM,Original Equipment Manufacture) 生产 7 nm SoC chipset圆芯片,例如苹果iphone 12 之A14 Bionic、华为 Mate 30之 Kirin 990 5G或三星 Galaxy S20之高通Smapdragon 865。这些极细小硅层架构之晶体管总量每平方毫米密度可高达一亿个级数

没有一间规模庞大垮国手机生产商有能力可以绕过这 (光刻蚀 – 代工) 讯息科技官僚体制运作,自行一家公司一手正向工序,生产4G或5G智能手机之主芯片组。总之,智能手机SoC chipset逆向工程眼前只是梦想,行不通的。

捷足先登,或俗语之 「赢在起跑线」, 或英谚语之 “Early bird catches the worm” ,都示意最先发明者最有机会掌握随着之发展。基于掌握最先进光刻机工艺核心技术,ASML紧握硅基SoC主芯片组OME量产之樽颈位。

(b) 干法蚀刻 (Dry etching) – 反应离子蚀刻 (Reactive Ion Etching,RIE) 和深反应离子蚀刻 (Deep Reactive Ion Etching,DRIE)工艺 (基于网上资料)

EUV光刻后段工艺是蚀刻,一般采用化学方法蚀去硅基质上不要之氧化物 (湿法蚀刻)。另一种蚀刻方法是干法蚀刻 (Dry etching) 。目前干法蚀刻采用反应离子蚀刻 (Reactive Ion Etching,RIE) 工艺。它利用高能等离子 (电浆体) 强化后的气体束轰击目标晶圆片,达到蚀刻目的。RIE蚀刻率竞争力不太强。近年开发了深反应离子蚀刻 (Deep Reactive Ion Etching,DRIE) 工艺,采用两个射频源:将等离子的产生和自偏压的产生分离,有效避免了RIE蚀刻中射频功率和等离子密度之间的矛盾。能够实现可控的侧向蚀刻,可以制作出陡峭或其他倾斜角度的侧壁。DRIE工艺步骤(Bosch工艺):钝化—蚀刻—钝化—蚀刻

How are microchips made

(3) IDM 模式制造 SoC Chipset

当在低晶体密度 IC 工艺年代,生产商一般采用 IDM 工序。现在极高晶体密度 IC 如SoC 主芯片组,整个制造流程都不可能由单一垮国企业承办。芯片设计、光刻、蚀刻、包装和测试是由不同制造商承办。这不是经济贸易问题,而是由于要批付众多专利权和克服极高要求工艺如光刻工序,并不是某一大厂家可以自家应付得来。因此出现了代工制造 (OEM) 微工序生产行业,分工合作制造SoC主芯片组。

中国经数十年改革开放发展,至2019年,与美国地缘政治实力变化激发巨大差异。美国要遏制中国国力崛起,起初只是互相提升贸易关税壁垒,后再因中国在潜有巨大商机和军备发展之5G网络通讯建设取得国内外快速发展,极有机会主导全球5G通讯建设标准。基于恐惧微电子高科技领域优势消失,美国因此瞄准堵截SoC 主芯片组代工制造环节,即中国 SoC 主芯片组制造弱项,作为弄糟中国之5G发展。接着华为发现不可以从ASML输入EUV光刻机和找台积电代工5G 麒麟系列SoC 主芯片组。不过华为也实时发马后炮向联发科技 (Media Tek Inc,MTK,也要台积电代工) 购入1.2亿天玑 (Dimensity) 芯片作储备,为未来两年5G手机SoC芯片做备胎。

2020年中国反击,定下 「双经济循环」政策 (主要应付新冠肺炎疫情国内受控国外纠缠下之后续世界新经济情况) ,其中一环节致力于攻克IDM制造nm工艺SoC主芯片组之高科技要求。例如力挺中芯国际OEM量产nm晶圆片。以当前国力而言,从长远的观点来说,克服EUV光刻工艺这弱项是有望成功的。2020中国科学院苏州纳米技术与纳米仿生研究所 (中科院苏州纳米所,CAS- SINANO) 研发双激光无掩模纳米级光刻工艺,有别于ASML之EUV photoresist masking光刻工艺。有希望数年时间后可以摆脱ASML制肘,主自IDM生产nm级数SoC 主芯片组,应付智能手机功能日新月异之市场要求。

2020年传统IC品牌 Intel 公司宣告自主 IDM 7 nm芯片生产计划,不用外工OEM厂商如台积电或三星。但尝试也不是一帆风顺。

(4) “碳基电子逻辑闸” 和 “分子逻辑闸电路” 之开发

最新探究之「碳基电子逻辑闸」(网上搜寻) 很有可能取代硅基电子逻辑闸,发展为另一途径生产先进 SoC chipset。2020中科院团队分别成功研制石墨烯基质高速半导体和石墨烯单晶晶圆。有鉴于目前或将来科技都极难克服1 nm或小于1 nm光刻技术,硅基SoC主芯片组研发至2 nm光刻阶段很可能会停顿下来。那时后硅基 SoC主芯片组年代智能手机市场将会由碳(石墨烯)基 SoC主芯片组厂商主导。从企业家角度看,若生产线开始建基于硅基微组装,则没有可能改为碳基微组装,因为所有设施皆用硅基技术,就算要面对死胡同也要面对。

China’s endeavor in carbon-based chip development

另一可能预见的进展是实现 “分子逻辑闸电路”,无界面耦合人体器官,进行各类前所未有之医疗疗程 。目前硅基SoC系统单芯片设施如何微型复杂化也不可能无界面植入人体器官 (回顾 28-29页: 神秘的人脑记忆机理)。

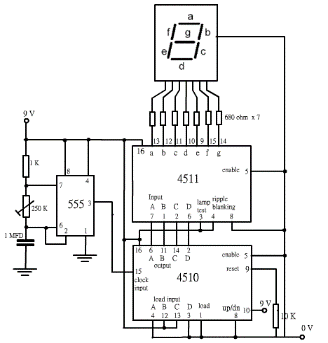

9.4电子制作:数字频率显示器

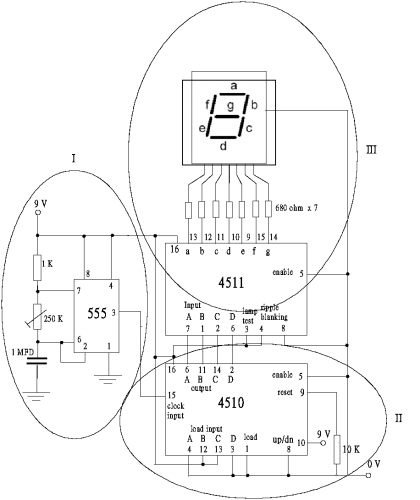

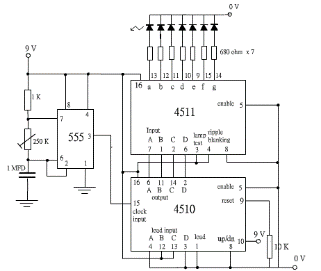

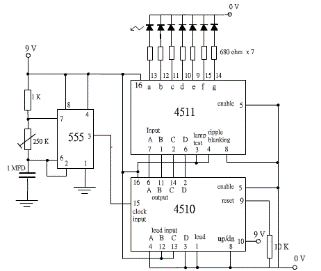

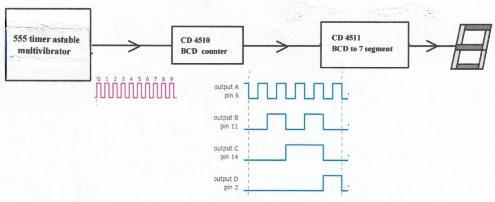

数字电子显示往往令人想起 0至 9之各种变化。当我们掌握了各类电子零件使用技巧后,便可以计设一电路满足这方面要求。换句话说,就是装组一数字频率显示器。显示0至9数字之各种变化。电路可分拆为三部份 (模块) ,在面饱板上完成装坎。

(1) 第一模块为时钟产生器,提供时基。

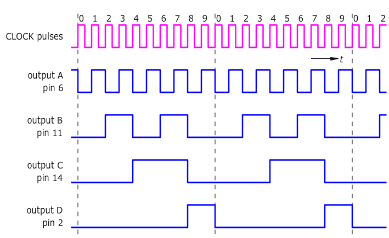

(2) 第二模块把产生之 (0 1) 频率时基配合一枚 IC (CD 4510),输出 BCD (Binary Coded Decimal),即 4-bit 讯号。

(3) 第三模块采用 IC CD 4511,转 BCD 4-bit 讯号输入为 abcdefg 7-bit 输出,再由abcdefg 7-bit 推动7 节目字形LED 作数字显示。

整体线路 (模块化)

|

| (图 268) 0至9数字频率显示模块电路 |

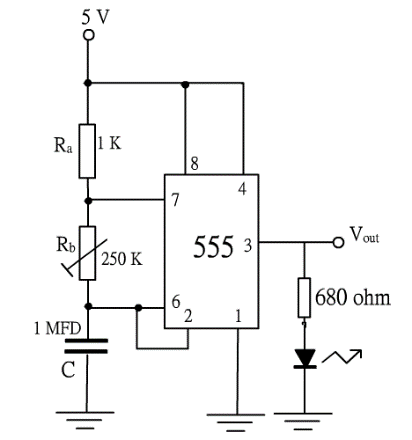

(i) 模块 (1) – 555无稳态振荡器

首先需要一个时基。555 IC 是专为产生时基而设计,广受用家欢迎。线路需要一个数 Hz 自发脉冲讯号。第一模块线路之 555 IC、1K (Ra)、250 K (Rb) 可变电阻和 1mF (C) 电容组成无稳态 (即自发) 振荡,频率为 f = [1.443/ (Ra + 2Rb) (C)] Hz 。

时基频率变动一般采用改变 Rb 之阻值方法而不是改变电容 C 之大小容量。以 (图 269) Ra = 1000Ω,Rb 可变电阻 = 250 KW ,C = 1mF 代入公式计算,LED 光暗频率可调校由 1443 Hz 至 2.88 Hz。

(图 269) LED光暗脉冲频率显示

注意:

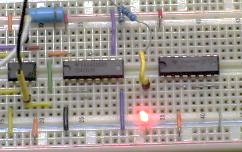

(a) 不建议一开始便接好整个数字频率显示器电路。应一模块一模块地连接并测试。先接好第一模块线路,检测555输出 (图269)。看看输出LED有否起振。

(b) 555电源是 5 V。9 V电源会烧毁单一LED,也影响输出频率。

555 ocillator

(ii) 模块 (2) –加入 CD 4510 BCD 4–bit计数器

(图 270) CD 4510内部结构

|

(图 271) 4 个独立 LED显 示 ABCD 输出 |

CD 4510 BCD4 bit output

接着把起振模块 (1) 连接模块 (2),即 BCD 4-bit 计数器。555 第3和4脚分别接CD 4510 第15和16脚。CD 4510 是一枚 BCD 计数器,会按脉冲输入演绎成 BCD 编码 (图 268),输出 4-bit (ABCD) 字节,其真值表如下s:

| 脉冲 | CD 4510 (BCD counter) 输出 0 表示暗,1 表示光 | |||

| A | B | C | D | |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 2 | 0 | 1 | 0 | 0 |

| 3 | 1 | 1 | 0 | 0 |

| 4 | 0 | 0 | 1 | 0 |

| 5 | 1 | 0 | 1 | 0 |

| 6 | 0 | 1 | 1 | 0 |

| 7 | 1 | 1 | 1 | 0 |

| 8 | 0 | 0 | 0 | 1 |

| 9 | 1 | 0 | 0 | 1 |

| 10 | 0 | 0 | 0 | 0 |

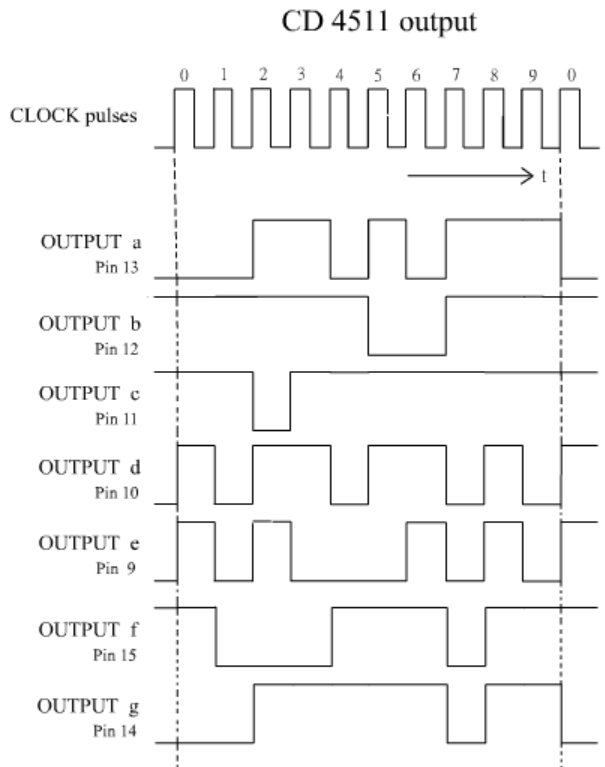

(iii) 模块 (3) –加入转 BCD 输入为 abcdefg 7-bit 输出

接着把ABCD 4-bit转为abcdefg 7-bit输出,作用是推动7节目形 LED 显示 0至9数字。其布尔真值表为:

| BCD 输入 | 7 节输出 | |||||||||

| A | B | C | D | a | b | c | d | e | f | g |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

转化需要软件演绎。但因其使用太普遍,厂家把程序转为硬件,以CMOS IC 出售。CD 4511 BCD to 7-segment CMOS 便是这用途之表表者。

(图 272) CD 4511 内部结构

(图 273) 7个独立LED显示 abcdefg 7-bit 输出

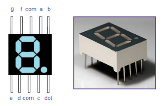

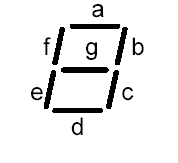

(iv)模块 (3)续 – 转abcdefg 7–bit 输出为7节日字 LED 数字显示

最后要把 abcdefg 7-bit 输出点亮 7 节日字形 LED,显示数字。7 节日字形 LED 有共阳极和共阴极两类,有红色或绿色选择。

|  |

0.56” 共阴极 7 节日字形 LED 第 3 或 8 脚接 0 V,3 V接第 1 脚点亮 e 节,第 2 脚点亮 d 节,第 4 脚点亮 c 节,第 5 脚点亮句号,第 6 脚点亮 b 节,第 7 脚点亮 a 节,第 9 脚点亮 f 节,第 10 脚点亮 g 节。 | |||||||||

| 7节输出 | 数字显示 | ||||||||

| a | b | c | d | e | f | g | |||

| 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | ||

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | ||

| 1 | 1 | 0 | 1 | 1 | 0 | 1 | 2 | ||

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 3 | ||

| 0 | 1 | 1 | 0 | 0 | 1 | 1 | 4 | ||

| 1 | 0 | 1 | 1 | 0 | 1 | 1 | 5 | ||

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 6 | ||

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 7 | ||

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 8 | ||

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 9 | ||

(图 274) 完整之7 节 LED 连续显示 0 至 9 数字线路

(图 275) abcdefg 7-bit 推动 7 节 LED

显示实时方形脉冲讯号输出如下图:

上图可如下理解:

0脉冲 :开始振荡 CD 4510 输出端为 (0 0 0 0),CD 4511输出端为 (1 1 1 1 1 1 0)

第1脉冲:CD 4510 输出端为 (1 0 0 0),CD 4511输出端为 (0 1 1 0 0 0 0)

第2脉冲:CD 4510 输出端为 (0 1 0 0),CD 4511输出端为 (1 1 0 1 1 0 1)

第3脉冲:CD 4510 输出端为 (1 1 0 0),CD 4511输出端为 (1 1 1 1 0 0 1)

第4脉冲:CD 4510 输出端为 (0 0 1 0),CD 4511输出端为 (0 1 1 0 0 1 1)

第5脉冲:CD 4510 输出端为 (1 0 1 0),CD 4511输出端为 (1 0 1 1 0 1 1)

第6脉冲:CD 4510 输出端为 (0 1 1 0),CD 4511输出端为 (0 0 1 1 1 1 1)

第7脉冲:CD 4510 输出端为 (1 1 1 0),CD 4511输出端为 (1 1 1 0 0 0 0)

第8脉冲:CD 4510 输出端为 (0 0 0 1),CD 4511输出端为 (1 1 1 1 1 1 1)

第9脉冲:CD 4510 输出端为 (1 0 0 1),CD 4511输出端为 (1 1 1 0 0 1 1)

整个流程如下图:

4510 第8脚 (up/down) 可提供由 0至9连续由低至高显示,即第 8 脚接地 (0),或由9至0连续由高至低显示,即第8脚接电源9V。

Up-counting 0 to 9

Down-counting 9 to 0

若改变250 K可变阻阻值,数字显示频率可调高。

Varying speed counting 0 to 9

数字显示脉冲频率对初学者可说不简单,不能以单一线路完成。不过正是如此,所有数字电路都应如此分析。基夲上,所有数字线路只是关乎高/低压电子开/关和一脉冲时基之复杂关系。